Tie cells are not present in the synthesized netlist and not placed in the initial placement of the standard cells. ASIC Design Methodologies and Tools Digital A SOLVED Why tap cells End caps Tie highlow cells are used in Physical Design flow.

Physical Only Cells Vlsi Physical Design For Freshers

In Physical design we prefer to add the spare cells using tool command.

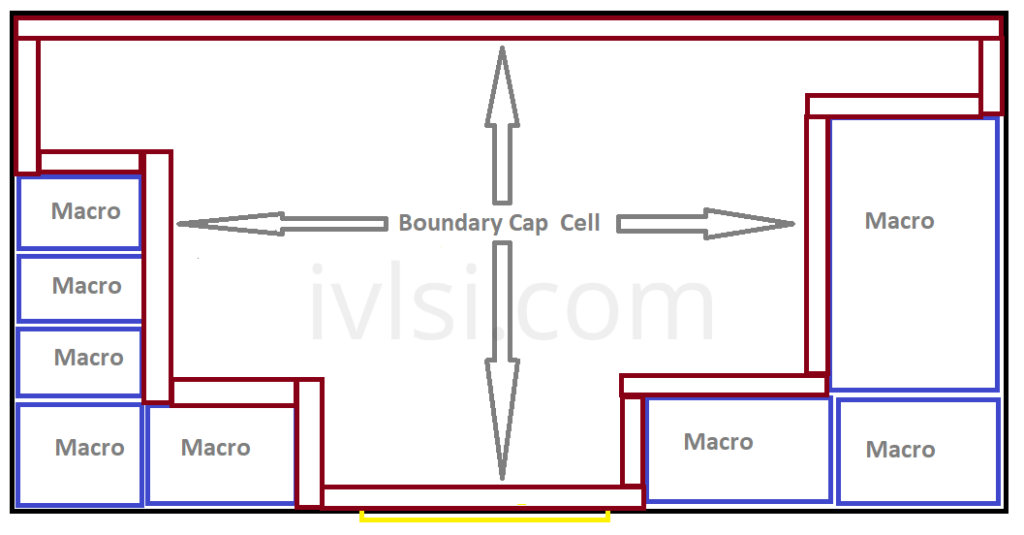

. End cap cells are required for certain technologies which require a well ring around your digital circuit. Boundary cap cells are physical only cells. What is Boundary Cap End Cap.

Boundary cells consist of end-cap cells which are added to the ends of the cell rows and around the boundaries of objects such as the core area hard macros blockages and voltage areas and corner cells which fill the empty space between horizontal and vertical end-cap cells. These cells essentially act as a capacitance between power and ground rails and hence as a charge reservoir that can be counted upon while there is a high demand for current from the power lines. Well tap cells or Tap cells are used to prevent the latch-up issue in the CMOS design.

Due to this short circuit condition a low impedance path is created. EndCap cells in Physical Design Flow. Filler Cells Once you have completed placement and routing there are usually gaps left in the layout where you do not have any standard cells present.

Well Tap cells are physical only cells which are placed in the design to avoid latch-up condition and maintain VDD and VSS NWELL continuity. The way of adding spare cells for Innovus and ICC tool has been explained below. There are various reasons for the instant large current requirement in the circuit and if there are no adequate measures have taken to handle this requirement power.

As per SOC Encounter user guide End-cap cells are preplaced physical-only cells required to meet certain design rules placed at the ends of the site rows. Filler cells have the WELL geometries to fill in the gaps. Decap Cells Decoupling capacitors are another type of physical only cells used in PD flow.

Well tap cells connect the nwell to VDD and p-substrate to VSS in order to prevent the latch-up issue. Filler Cells Well Tap Cells Decap Cells. They connect only to the power and ground rails once power rails are created in the design.

DeCap Cells in Physical Design Use of Decap Cells in PD. To avoid drain and source short. You dont really require endcap cells.

It is not possible to abut every cell available as that would cause. End cap Cells. Similarly endcap cells has the well geometry to make a ring around your core and touching the existing well.

Used for row connectivity and specifying row ending. ASIC Design Methodologies and Tools Digital L SOLVED physical layout in. Decap cells are basically a charge storing device made of the capacitors and used to support the instant current requirement in the power delivery network.

Latch-up basically means a short circuit condition between power and ground. We cant have functional failure in our design. Where ever netlist is having any pin connected to 0 logic or 1 logic like A 1b0 or IN 1b1 a tie cell gets inserted there.

They also ensure that gaps do not occur between the well and implant layers. Boundary cap cells are placed just after macro placement in the floorplan flow. So to avoid any kind of functional failure.

In some technologies they serve for power distribution as well. Placement of Spare cells. Tie cells are inserted in the placement stage and more specifically at the final stage of placement.

These do not have any logical functionality. Decap cell is basically a capacitor cell which is used temporarily in the design between power and ground rails to counter the functional failure. Spare cells can be added either by the netlist or by PnR tool command or GUI too.

These are used to address boundary N-Well issues for DRC cleanup. Fig1 End-cap cells are typically nonlogic cells such as a decoupling capacitor for the power rail. END CAP CELLS End cap cells are pre placed physical only cells it has only physical connectivity End cap cells are placed at the end.

The library cells do not have cell connectivity as they are only connected to power and ground rails thus to ensure that gaps do not occur between well and implant layer and to prevent the DRC violations by satisfying well tie-off requirements for core rows we use end-cap cells. Tap Cell Placement. These cells are placed at the periphery of the core and power domain.

Let us continue with the physical only cells present in the standard cell libraries that ease the digital PD flow. End Caps End-cap cells are preplaced physical-only cells required to meet certaindesign rules and placed at the ends of the site rows by satisfying well tie-off requirements for the core rows These library cells do not have any signal connectivity They connect only to the power and ground rails once power rails are created in the design. Standard Cells ICG Cells Well Taps End Caps Filler Cells Decap Cells ESD Clamp Spare Cells Tie Cells Delay Cells Metrology Cells IO Design IO Pads Input Output Pads Structure of Pad Implementation Guidelines Pad Limited Design Core Limited Design Types of IO Pads Staggered IO Pads Flip Chip IO Bumps Delay Models Delay Calculation Delay Models.

These cells are added before the placement of standard cells throughout the design. VLSI Physical Design. There is no logical function in well tap cell rather than proving a taping to nwell and p-substrate therefore well tap cell is called a physical-only cell.

Placements checks Congestion If the congestion is there in your design first check in which region you got the congestion hotspot If it is with cell density u. These cells prevent the cell damage during fabrication. End Cap Cells VLSI Physical Design Tuesday 20 October 2015 End Cap Cells These library cells do not have signal connectivity.

Welcome To The World Of Physical Design Different Types Of Physical Cells

End Cap Or Boundary Cell Use Of Endcap Cells Placement Of Endcap Cell Layout Of Endcap Cell Youtube

Physical Only Cells Vlsi Physical Design For Freshers

Physical Only Cells Vlsi Physical Design For Freshers

Team Vlsi End Cap Cells In Vlsi Boundary Cells In Vlsi

0 comments

Post a Comment